# efficēon

# Software Configuration Guide

Transmeta™ Efficeon™ TM8x00

Hardware Revision 1.x

Code Morphing™ Software Version 6.x

Transmeta PROPRIETARY Information Provided Under Nondisclosure Agreement

Preliminary Information—SUBJECT TO CHANGE

September 10, 2003

#### Property of:

Transmeta Corporation 3990 Freedom Circle Santa Clara, CA 95054 USA (408) 919-3000 http://www.transmeta.com

The information contained in this document is provided solely for use in connection with Transmeta products, and Transmeta reserves all rights in and to such information and the products discussed herein. This document should not be construed as transferring or granting a license to any intellectual property rights, whether express, implied, arising through estoppel or otherwise. Except as may be agreed in writing by Transmeta, all Transmeta products are provided "as is" and without a warranty of any kind, and Transmeta hereby disclaims all warranties, express or implied, relating to Transmeta's products, including, but not limited to, the implied warranties of merchantability, fitness for a particular purpose and non-infringement of third party intellectual property. Transmeta products may contain design defects or errors which may cause the products to deviate from published specifications, and Transmeta documents may contain inaccurate information. Transmeta makes no representations or warranties with respect to the accuracy or completeness of the information contained in this document, and Transmeta reserves the right to change product descriptions and product specifications at any time, without notice.

Transmeta products have not been designed, tested, or manufactured for use in any application where failure, malfunction, or inaccuracy carries a risk of death, bodily injury, or damage to tangible property, including, but not limited to, use in factory control systems, medical devices or facilities, nuclear facilities, aircraft, watercraft or automobile navigation or communication, emergency systems, or other applications with a similar degree of potential hazard.

Transmeta reserves the right to discontinue any product or product document at any time without notice, or to change any feature or function of any Transmeta product or product document at any time without notice.

Trademarks: Transmeta, the Transmeta logo, Crusoe, the Crusoe logo, Efficeon, the Efficeon logo, Code Morphing, LongRun, and combinations thereof are trademarks of Transmeta Corporation in the USA and other countries. Other product names and brands used in this document are for identification purposes only, and are the property of their respective owners.

Copyright © 2003 Transmeta Corporation. All rights reserved.

# Directory of Contents

|            | Directory of Tables                   | 5  |

|------------|---------------------------------------|----|

|            | Directory of Figures                  | 7  |

| Chapter 1  | Code Morphing Software Overview       | 9  |

| onapto     |                                       |    |

| Chapter 2  | Code Morphing Software Image          |    |

|            | 2.1 Hardware Environment              |    |

|            | 2.2 Software Environment              |    |

|            | 2.3 Configuration Overview            |    |

|            | 2.3.1 ROM Sections                    |    |

|            |                                       |    |

| Chapter 3  | Memory Configuration                  |    |

|            | 3.1 DIMM Slots                        |    |

|            | 3.2 Required Memory Configuration     |    |

|            | 5.5 Optional Memory Configuration     | 19 |

| Chapter 4  | OEM Configuration Table               | 23 |

| •          | 4.1 Read-Only Fields                  |    |

|            | 4.2 OEM-Managed Fields                | 26 |

|            | 4.3 Transmeta SKU Fields              | 34 |

| Chapter 5  | Code Morphing Software: Initial State | 43 |

| Chapter 6  | Code Morphing Software: Examples      | 45 |

| Chapter 7  | Code Morphing Software: Checklist     | 47 |

| Appendix A | POST Codes                            | 49 |

| Appendix B | Recommended Reading                   | 51 |

|            | Glossary                              | 53 |

|            | Index                                 | 63 |

# Directory of Tables

| Table 1: | Header Fields                               | 24 |

|----------|---------------------------------------------|----|

| Table 2: | OEM-Managed Fields                          | 26 |

| Table 3: | Transmeta SKU Fields                        |    |

| Table 4: | OEM Configuration Table Initial State       | 43 |

| Table 5: | Efficeon TM8000 POST Codes in Receipt Order | 49 |

# Directory of Figures

| Figure 1: | Efficeon Package in a Bringup or Debugging Environment | 12 |

|-----------|--------------------------------------------------------|----|

| Figure 2: | Code Morphing Software Image as a Software Component   | 13 |

Chapter 1

# Code Morphing Software Overview

The following chapters provide information necessary to configure Code Morphing<sup>™</sup> software (CMS), the software portion of the Efficeon<sup>™</sup> TM8x00 processor.

#### **Reference Documents**

The following documents should be used in conjunction with this guide:

- Efficeon™ Processor Data Book

- Efficeon™ Processor BIOS Programmer's Guide

- Efficeon™ Processor Bringup and Configuration Tools

- Efficeon™ Processor System Design Guide (Preliminary)

- JEDEC Standard No. 21-C (11/25/97)

#### Changes from 7/10/03 Revision

- Updated entire document with Efficeon markings.

- · Updated Chapter 2, Code Morphing Software Image.

- · Added Chapter 3, Memory Configuration.

- Updated Chapter 4, OEM Configuration Table. Added documentation for the several fields.

- Added Chapter 5, Code Morphing Software: Initial State.

- Added Appendix A, POST Codes.

Chapter 2

# Code Morphing Software Image

This chapter describes the Code Morphing™ software image and how to create it. This chapter also provides an overview of the process of bringing up an Efficeon processor in a development laboratory or preproduction environment, and configuring it correctly for production.

The nature of an Efficeon processor is different from other products of its class in two significant ways:

- Parts of the processor itself are implemented in software. This enables many features not feasible in hardware-only processors. For example, upgrades can be devised that involve a customer simply executing a small, downloadable utility to flash a "processor upgrade" into ROM, with no swapping motherboards or soldering required.

- The processor converts application code, in particular x86 code, into its own machine code on the fly.

This enables the processor to emulate other popular processors.

These innovations require different configuration techniques from other types of processors. There are several steps required to bring up and configure a Transmeta Efficeon processor. In addition, there are policies for memory layout, future processor upgrades, and other features that must be decided.

Code Morphing software provides many innovative services such as dramatically improved power management and thermal management capabilities (LongRun™), a Virtual Northbridge (VNB) that eliminates the need for a hardware northbridge, and a translation caching mechanism that enables the processor to "learn" how users interact with their applications and increase actual working speed while running.

Since Code Morphing software loads and runs even before the BIOS, it must reside in a ROM where the processor can find it and boot from it. Generally, you create a Code Morphing software image with a Transmeta-supplied utility, then upload this image into the ROM using a ROM programmer or a Transmeta-supplied device (see the book *Efficeon™ Tools Guide*). The new image is used to boot the system on reset.

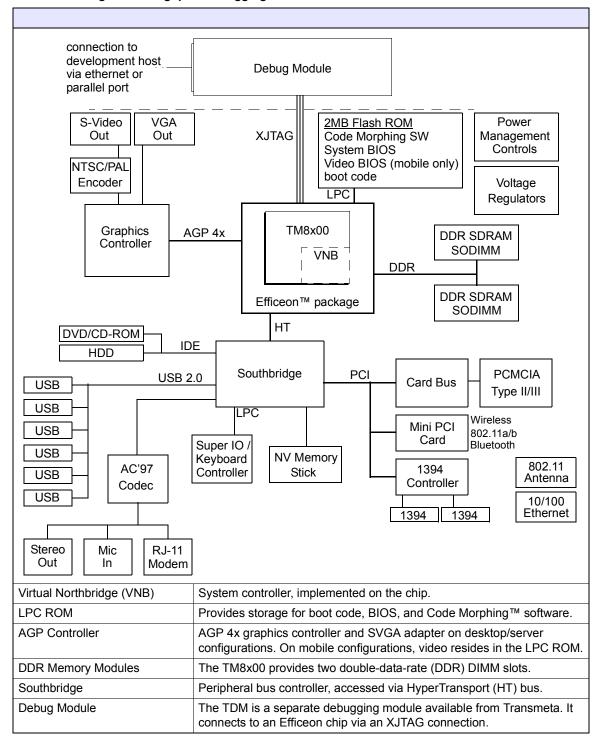

## 2.1 Hardware Environment

In general, an Efficeon chip resides in a framework where it communicates with a southbridge via an HT bus, a flash LPC ROM module via an LPC bus, a graphics module via an AGP bus, and a DDR RAM memory module. Northbridge functions such as power and memory management are provided on the Cruose package in a Virtual Northbridge (VNB)—no separate hardware northbridge is necessary. Code Morphing™

Software, which translates x86 instructions into VLIW instructions for the processor, resides with the BIOS in a serial ROM accessed by LPC.

The following diagram shows the Efficeon package laid out with other necessary components, including the Transmeta Debugging Module (TDM). (For more information on the TDM, see the *Efficeon Tools Guide*.) Note that this diagram is for illustrative purposes only; for a detailed discussion of the hardware environment, including true schematic diagrams, see the *Efficeon TM8x00 System Design Guide*.

Figure 1: Efficeon Package in a Bringup or Debugging Environment

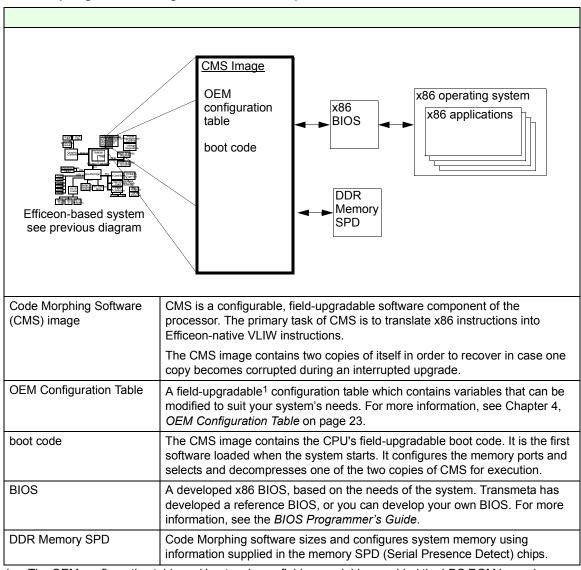

## 2.2 Software Environment

Unlike most other microprocessors, the Efficeon core also contains a robust software environment that handles many tasks that are controlled by hardware on other platforms. The centerpiece of this design is Code Morphing™ software (CMS), which provides a translation service from x86 code to Efficeon-native VLIW code.

The following diagram shows the arrangement of the Code Morphing software image in the Efficeon package.

Figure 2: Code Morphing Software Image as a Software Component

<sup>1.</sup> The OEM configuration table and boot code are field-upgradable, provided the LPC ROM in use has its bottom 64kb split into independently-erasable 4kb sectors. For more information, see TBD.

## 2.3 Configuration Overview

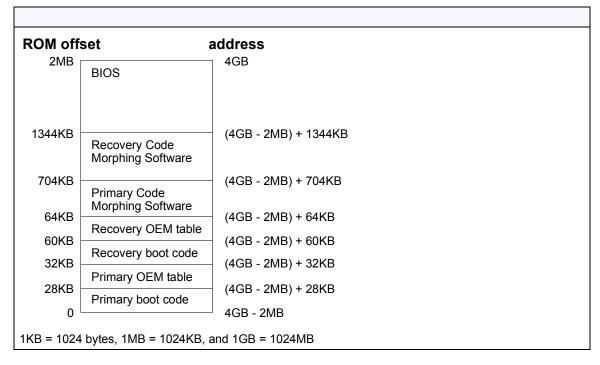

#### 2.3.1 ROM Sections

A 2MB (16 Mbit) Code Morphing software ROM image consists of several logical components, described below.

The non-BIOS components of CMS are readable through x86 space at these addresses if ROM windows in the northbridge are programmed appropriately.

- Boot code. These are the first native (VLIW) instructions executed upon reset. It includes some poweron self-test (POST) code and a decompressor, necessary because Code Morphing software is stored in compressed form. Also contains memory configuration code.

- Code Morphing software. This software translates x86 instructions from the operating system, applications, drivers, etc. into VLIW instructions for the processor, using configuration information found in the OEM configruation table.

- OEM configuration table. This is a data structure programmed by the OEM/ODM to control several

aspects of the behavior of the CPU, the boot code, and Code Morphing software.

- Recovery boot code/OEM configuration table/Code Morphing software. Backup copies of each of the main components of the image.

## 2.3.2 Creating a CMS Image

A CMS image is created by first programming the OEM configuration table by editing the OEM configuration template, and then compiling an image with the Transmeta-supplied utility makerom. The image is uploaded to the LPC ROM using the utility flashtool, and the system is rebooted.

For information about makerom, flashtool, and other Transmeta utilities, see the Efficeon Tools Guide.

Chapter 3

# Memory Configuration

There are several parameters in the OEM configuration table that affect memory configuration by the Code Morphing software boot code. This chapter outlines memory configuration parameters from a hands-on perspective.

Refer to Chapter 4, OEM Configuration Table on page 23 for more details on individual parameters.

### 3.1 DIMM Slots

The Efficeon memory controller supports up to 4 logical DIMMs. That is, although it supports 8 *ranks* of memory, the ranks are collected into one-ranked or symmetric two-ranked DIMMs. That is, there is no way to have 8 independent ranks. At most there are 4 DIMMs, each two-ranked, but the two ranks in each DIMM have to be equal, i.e., same kinds of chips and organizations on both ranks of a DIMM.

This is independent of whether physical (So)DIMMs or soldered-down memory are used. In other words, even if memory is soldered down, it must be described to the controller as a logical DIMM that may be one-ranked or two-ranked, but if it is two-ranked, then the two ranks have to be identical.

Thus the memory configuration code is organized around the concept of *DIMM slots*, which are the logical places where a DIMM is connected. Of course, for soldered-down memory there is no physical DIMM slot, but there is still the concept, and this is how the memory is described to the software and the controller.

Note that although the controller supports up to 4 logical DIMMs, it can not support 4 physical DIMMs because it does not have enough clock pairs for the general case. In specific configurations (registered DIMMs only use one clock pair) and specific boards, it may support 4. Nothing above two is supported at this time, but the controller and the software is forward-compatible in case a reference design without these constraints is created at some point.

## 3.2 Required Memory Configuration

Following is the short list of parameters that OEMs are expected to set, all in the OEM-Managed section of the configuration table:

- mem probe spd (also see mem probe spd on page 28)

- mem\_sbus\_spd\_base\_addr (also see mem\_smbus\_spd\_base\_addr on page 28)

- mem\_slot\_to\_clocks[4] (also see mem\_slot\_to\_clocks[4] on page 28)

- mem\_spd[4] (also see mem\_spd[4] on page 29)

#### mem\_probe\_spd

mem\_probe\_spd is a 4-bit bitmask that tells the boot code whether to read SPD data from the SPD ROM in a DIMM, or from the OEM configuration table. There is one bit per logical DIMM slot (4 theoretically). Bit 0 of the bitmask corresponds to slot 0, and so on.

A bit value of 0 means that the SPD data is to be found in the OEM config table, i.e. this 'DIMM slot' is a soldered-down DIMM and we are using the OEM config table to contain the SPD data rather than soldering down a separate SPD ROM.

A bit value of 1 means that the SPD data is to be found in the SPD ROM for this DIMM slot. In real terms, this "DIMM slot" is a true DIMM slot that can have an arbitrary DIMM inserted into it, or otherwise looks enough like a DIMM that it has a separate SPD ROM readable through the SMBUS.

Transmeta's current reference design boards have two DIMM slots (slots 0 and 1) and no soldered down memory. Thus we use the default value 3 (binary 0011), to make the boot code read SPD data from the SMBUS for slots 0 and 1, and from the OEM configuration table for slots 2 and 3 (but see mem\_slot\_to\_clocks below).

### mem sbus\_spd\_base\_addr

mem\_smbus\_spd\_base\_addr is the SMBUS address of the SPD ROM for slot 0. The other SPD ROMs are assumed to be at increasing SMBUS addresses from this one. Note that if slot 0 is soldered-down, but slot 1 really has a DIMM slot, this field still needs to contain the SMBUS address that slot 0 would have used, i.e. 1 less than the SMBUS address for slot 1.

For Transmeta's current reference design boards, the value is 0x50 (decimal 80) meaning that the SPD ROM for DIMM slot 0 is at SMBUS address 0x50, the SPD ROM for DIMM slot 1 is at address 0x51, etc.

#### mem\_slot\_to\_clocks[4]

mem\_slot\_to\_clocks[4] is an array of 4 8-bit bitmasks. This array tells the boot code what clock pairs to enable for each DIMM slot that is present.

If a slot has no clocks, then the boot code assumes that that slot is not present and does not try to configure it. Similarly, if the boot code decides that there is no memory in some DIMM slot, it does not turn its clocks on, to save a little power. On Transmeta's current reference design boards, the clocks are set to 0 for slots 2 and 3 in order to turn them off.

Each clock pair is represented by a bit in an 8-bit bitmask. Clock pair 0 corresponds to bit 0 and clock pair 7 corresponds to bit 7.

DIMMs generally require 3 clock pairs each. A board designer can use any 3 of the 8 available clock pairs and needs to inform the boot code of which pairs are used for which DIMM slot. On Transmeta's current reference design boards, clock pairs 0-2 are used for slot 0, clock pairs 3-5 are used for slot 1, and clock pairs 6 and 7 are unused.

Thus, mem slot to clocks[4] defaults to { 0x07, 0x38, 0, 0 } for Transmeta's current reference design boards.

If a designer solders down some memory, clock pair assignments may differ, and there mayb be fewer than 3 clock pairs for the soldered-down memory. For example, on a hypothetical board with a soldered-down DIMM slot using clock pairs 0 and 1, and two DIMM slots using clock pairs 2-4 and 5-7 respectively, the board would have mem slot to clocks[4] set to { 0x3, 0x1c, 0xe, 0 }.

#### mem spd[4]

mem\_spd is an array of 4 SPD data structures. An element of mem\_spd is only used when the corresponding bit in mem\_probe\_spd is 0. This is where an OEM provides SPD data to the boot code for soldered-down memory.

Note that Efficeon only uses the first 64 bytes of the SPD data, so mem\_spd only has room for those 64 bytes, which include the checksum for those 64 bytes. If an OEM only has true DIMM slots, these fields need not be programmed. This is the case for Transmeta's current reference design boards.

The recommendation for setting SPD data for soldered-down memory is to obtain a SoDIMM that has the same chips and configuration as the soldered-down memory, read the first 64 bytes of the SPD data out of the DIMM, and then program those bytes into the appropriate slot in the OEM config table. Otherwise, Transmeta maintains a set of canonical SPD data files that can be used, but it is best to use the manufacturer's data.

The default for this fields is all zeros since they are unused with Transmeta's current reference design boards.

## 3.3 Optional Memory Configuration

The default memory configuration parameters are designed to work for all OEMs. However, in case of problems, this section describes parameters that can be adjusted, with Transmeta's help, to tune the boot code to an OEM's board. DO NOT change any of these parameters without help from Transmeta engineers.

- cpu feature (also see cpu\_feature on page 27)

- mem\_freq\_min (also see mem\_freq\_min on page 30)

- mem\_freq\_max (also see mem\_freq\_max on page 30)

- sclkdly\_to\_mem\_frequency[4] (also see sclkdly\_to\_mem\_frequency[4] on page 32)

- group\_to\_min\_loads[4] and group\_to\_max\_loads[4] (also see group\_to\_min\_loads[4] on page 32 and group\_to\_max\_loads[4] on page 33)

#### cpu\_feature

cpu\_feature contains two bits that affect memory configuration that OEMs may want to use.

- Bit disable\_ecc means that ECC should not be used even if all the DIMM slots support ECC. This is used

in Transmeta's current reference design boards by default because of the performance problems

associated with using ECC. The default for OEM boards is disabled (1).

- Bit SSTL2\_termination means that the board has SSTL\_2 termination for the signals (command, address, data, and strobes). This bit should not be necessary since the boot code should configure memory automatically either way, but it may be necessary in some boards of hardware revision 1.1. We recommend that customers not use SSTL\_2 termination on rev. 1.1 hardware, so the default is off (0).

#### mem\_freq\_min

mem\_freq\_min specifies a frequency below which the boot code does *not* configure memory. The frequency is specified in multiples of 16.67 MHz. and limits the command frequency of the DDR bus (e.g. 133 MHz for DDR266 = PC2100, 200 MHz for DDR 400 = PC3200).

The boot code tries to configure memory at the highest rated speed (unless clamped by mem\_freq\_max or some characterization fields). If configuration fails at that speed, the boot code decreases the speed of the memory in 16.67 MHz or 33.33 MHz steps until it finds a working configuration. If at some point it tries to go below mem freq min, it fails.

The default is 5, encoding 83.3 MHz, which is the minimum speed according to the JEDEC specs for DDR200, DDR266, and DDR333. DDR400 may have a minimum speed of 100 MHz, which would be encoded as 6.

#### mem freq max

mem\_freq\_max specifies the maximum frequency to use for memory even if the installed memory supports higher frequencies. The frequency is specified in multiples of 16.67 MHz, and limits the command frequency of the DDR bus.

This allows an OEM, for example, to qualify a board with DDR266, and force the boot code to use 133 MHz frequency and not try higher speeds even if the memory supports it.

The default is 10, encoding 166.67 MHz (i.e. DDR333 = PC2700).

### sclkdly\_to\_mem\_frequency[4]

sclkdly\_to\_mem\_frequency is an array of four values specifying a mapping between memory frequencies and the internal sclkdly parameter.

sclkdly is a parameter used to compensate for board roundtrip time. A board with long DDR traces would require larger sclkdly values than a board with short traces. The sclkdly value controls the phase difference between the internal NB (Northbridge) clock and the external DRAM clock that the DRAM chips see. The DRAM clock can lead the Northbridge clock by up to 3/8 of a cycle.

Loosely speaking, an sclkdly value of N means that the DRAM clock leads the NB clock by N/8 cycles. Thus with a setting of 0, there is no phase difference between both clocks, while with a setting of 3, there is a 3/8 cycle difference between them. The larger the phase difference, the more round trip delay that can be

accomodated. However, the phase difference can't be made too large because otherwise data may return 'too soon'. At higher frequencies, the same 1/8 fraction of a cycle becomes less absolute time, so even though the board round-trip time may remain a constant, the fraction needs to be increased as well.

The encoding of sclkdly\_to\_mem\_frequencies is such that each element of the array encodes the highest memory command frequency value (in multiples of 16.67 MHz) that can use the value of the index of the element. The default, which works well with Transmeta's current reference design boards, is:

| Field                       | Value | Description                               |

|-----------------------------|-------|-------------------------------------------|

| sclkdly_to_mem_frequency[0] | 7     | 116.67 MHz is max frequency for sclkdly 0 |

| sclkdly_to_mem_frequency[1] | 10    | 166.67 MHz is max frequency for sclkdly 1 |

| sclkdly_to_mem_frequency[2] | 255   | oo is max frequency for sclkdly 2         |

| sclkdly_to_mem_frequency[3] | 255   | oo means that sclkdly 3 is unused         |

For boards with less round-trip time (e.g. with soldered-down memory close to the CPU), it is best to use 0 for higher frequencies (e.g. DDR266 encoded as 8, or even DDR333 encoded as 10), and so on.

For boards with more round-trip time (e.g. 4 DIMM slots very far away), it would be best to use 0 for lower frequencies (e.g. DDR200 encoded as 6, or even DDR167 encoded as 5), and so on.

#### group\_to\_min\_loads[4] and group\_to\_max\_loads[4]

group\_to\_min\_loads and group\_to\_max\_loads are best described together. Each is an array of four values used to control the drive strength for the different signal groups in Efficeon processors.

#### **Drive Strength Background**

Drive strength must be reasonably well matched to the actual load, especially for boards lacking SSTL\_2 termination. If the drive strength is too low, the signals rise and fall slowly and reduced frequency of operation may result. If the drive strength is too high, ringing and coupling can occur, and this also reduces the effective frequency of operation.

The Efficeon controller has programmable drive strength, where the configuration software (i.e. the boot code) can enable more or fewer drivers for each of four signal groups. The drive strength for each signal group is affected by the entries in these two arrays with the corresponding index.

- Group 0 is the clock signals (CLK, CLK#). The boot code assumes that there are always four effetive

loads for this signal group, as the JEDEC SoDIMM specs require the addition of capacitors to make all

clock pairs be similarly loaded.

- Group 1 is the per-rank commands signals (CS#, CKE). The boot code computes the loads per rank given the configuration of the DIMMs and assumes that all chips present the same load, so it determines drive strength given the rank with the largest number of loads (e.g. if one DIMM has 4 x16 parts and another has 8 x8 parts, it assumes 8 chip loads).

- Group 2 is the shared command and address signals (RAS#, CAS#, WE#, BA<1:0>, and address).

These signals are typically the most loaded as they go to every DRAM chip in every DIMM and rank, unless registered DIMMs are in use. The boot code sums the total number of DRAM chips given the actual configuration, and considers that the logical chip load for this signal group.

- Group 3 is the strobe and data signals (DQS and DQ). Each of these signals is loaded once per rank of memory, but each chip load is typically twice as large as the loads on the other signals.

#### **Specifying Drive Strength**

In the controller, drive strength is specified, per signal group, as a value between 0 and 7, both inclusive. Each of these values enables some progressive number of drivers for that signal group. The actual numbers of drive transistors used are:

group\_to\_min\_loads specifies, per signal group, the minimum logical chip loads that can be driven when the strength parameter is set to 0. Similarly, group\_to\_max\_loads specifies, per signal group, the maximum logical chip loads that can be driven when the strength parameter is set to 7. The boot code linearly interpolates between these sets of values, given the number of logical chip loads in each signal group.

Note that when lightly loaded (few logical chip loads), board capacitance may matter more than logical chip loads, while when heavily loaded (large number of chip loads), the logical chip loads is the dominant effect. Board capacitance partly determines drive strength. As different board layouts, routing, and materials can affect drive strength, the parameters are tunable by OEMs, with Transmeta's help.

The defaults are all-zeros for min\_loads, meaning that at their lowest setting we can drive no chip loads, and { 18, 18, 18, 9 } for max\_loads, meaning that at the highest setting, we can drive 18 logical loads for most signal groups, and only 9 logical loads for the DQ/DQS signal group. To allow for increased drive strength at the low end, these arrays contain signed values, so negative values can be used causing the drive strength to become higher.

Here are some examples of how the min, max, and logical chip loads results in a setting of drive strength:

|         | For min=4, max-18: |                | For m  | nin = 0, max = | 18:            |

|---------|--------------------|----------------|--------|----------------|----------------|

| N loads | N drivers          | Drive strength | N driv | /ers           | Drive strength |

| 1       | 1 -> 4             | 0              | 5      |                | 1              |

| 2       | 2 -> 4             | 0              | 6      |                | 2              |

| 3       | 3 -> 4             | 0              | 7      |                | 3              |

| 4       | 4                  | 0              | 8      |                | 4              |

| 5       | 5                  | 1              | 8      |                | 4              |

| 6       | 6                  | 2              | 9 ->   | 10             | 5              |

| 7       | 7                  | 3              | 10     |                | 5              |

| 8       | 8                  | 4              | 11 -   | > 12           | 6              |

| 9       | 9 -> 10            | 5              | 11 -   | > 12           | 6              |

| 10      | 10                 | 5              | 12     |                | 6              |

| 11      | 11                 | 6              | -> 1   | 8              | 7              |

| 12      | 12                 | 6              |        |                |                |

| 13+     | ->18               | 7              |        |                |                |

Note that for group 2 (shared command and address signals), the controller uses 'double command mode' when the number of logical chip loads exceeds the value in group\_to\_max\_loads[2].

Chapter 4

# OEM Configuration Table

The OEM configuration table provides an interface for manufacturers to edit various Code Morphing™ software settings, notably LongRun voltage/frequency points but also VRDA information and (optionally) memory settings to override SPD information. This table also provides boot code settings that were controlled by a mode bit ROM in previous Transmeta processors.

Manufacturers create a configuration table using a SKU provided by Transmeta as well as the manufacturer's decisions about various aspects of processor configuration. The table is encoded using a utility called ROM Compiler, and then uploaded with the BIOS to a ROM on the motherboard. Code Morphing software is the first software to run on the processor—it sizes memory, sets voltage and frequency points, and configures the processor prior to loading the BIOS and operating system.

OEM configuration table fields are categorized in this chapter as follows:

- OEM-Managed Fields on page 26

- Transmeta SKU Fields on page 34

- · Read-Only Fields on page 24

Each section provides a summary of all fields described in that section. All sizes shown are in bytes.

#### Field Access

Each field in this configuration table is listed as one of the following:

| RO | Read-only. Do not change these fields.                                                                                   |

|----|--------------------------------------------------------------------------------------------------------------------------|

| RW | Read-write. Change these fields to suit your application.                                                                |

| ТО | Transmeta-recommended values only. Contact your Transmeta representative to obtain the proper settings for these fields. |

#### Note

This configuration table is a work in progress, and many details are to be determined. This table described here is not to be used with any Transmeta processor without assistance from a Transmeta representative.

# 4.1 Read-Only Fields

The fields described in this section are read-only parameters that define the size and scope of Code Morphing software. They are administrative in nature and do not need to be changed by manufacturers.

#### Table 1: Header Fields

| Field Name                    | Table<br>Offset | Width (bytes) | Access | Default Value      | Page |

|-------------------------------|-----------------|---------------|--------|--------------------|------|

| header                        | 0x0000          | 16            | RO     | "OEM Config Table" | 24   |

| cpu_type                      | 0x0010          | 1             | RO     | 0x41               | 24   |

| format_rev_major              | 0x0011          | 1             | RO     | 0x04               | 24   |

| table_size                    | 0x0012          | 2             | RO     | 0x0C7C             | 25   |

| checksum                      | 0x0014          | 4             | RO     | checksum           | 25   |

| format_rev_minor              | 0x0018          | 4             | RO     | 0x00000001         | 25   |

| upgrade_compatibility_version | 0x001C          | 4             | RO     | 0x00000000         | 25   |

| timestamp                     | 0x0020          | 4             | RO     | 0x00000000         | 25   |

#### header

| Field Name | Table Offset | Width (bytes) | Access | Default Value      |

|------------|--------------|---------------|--------|--------------------|

| header     | 0x0000       | 16            | RO     | "OEM Config Table" |

String of characters demarcating the beginning of the OEM configuration table.

#### cpu\_type

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| cpu_type   | 0x0010       | 1             | RO     | 0x41          |

Processor type designation.

#### format\_rev\_major

| Field Name       | Table Offset | Width (bytes) | Access | Default Value |

|------------------|--------------|---------------|--------|---------------|

| format_rev_major | 0x0011       | 1             | RO     | 0x04          |

Primary format revision.

### table\_size

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| table_size | 0x0012       | 2             | RO     | 0x0C7C        |

Size of the defined part of the OEM configuration table.

#### checksum

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| checksum   | 0x0014       | 4             | RO     | checksum      |

Negated checksum of the entire table (total checksum = 0). This field should not be changed by hand.

#### format rev minor

| Field Name       | Table Offset | Width (bytes) | Access | Default Value |

|------------------|--------------|---------------|--------|---------------|

| format_rev_minor | 0x0018       | 4             | RO     | 0x0000001     |

Minor table revision number.

#### upgrade\_compatibility\_version

| Field Name                    | Table Offset | Width (bytes) | Access | Default Value |

|-------------------------------|--------------|---------------|--------|---------------|

| upgrade_compatibility_version | 0x001C       | 4             | RO     | 0x00000000    |

This bitfield identifies the potential compatibility of the running Code Morphing software version to possible upgrades. Each bit corresponds to one compatibility issue, to be defined in a future revision.

#### timestamp

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| timestamp  | 0x0020       | 4             | RO     | 0x00000000    |

Timestamp generated by Transmeta.

# 4.2 OEM-Managed Fields

The fields in this section can be changed by manufacturers to suit specific applications. See the individual fields for descriptions of their operation.

#### Table 2: OEM-Managed Fields

| Field Name                  | Table Offset | Width (bytes)  | Access | Default Value   | Pg |

|-----------------------------|--------------|----------------|--------|-----------------|----|

| vr_100mV_ramp_time          | 0x0100       | 2              | RW     | 0x0023          | 26 |

| vr_voltage[32]              | 0x0104       | 2 (64 total)   | RW     | See description | 27 |

| cpu_feature                 | 0x0144       | 4              | RW     | 0x00000002      | 27 |

| cms_memory_size             | 0x0148       | 1              | RW     | 0x20            | 28 |

| mem_probe_spd               | 0x0149       | 1              | RW     | 0x03            | 28 |

| mem_smbus_spd_base_addr     | 0x014a       | 1              | RW     | 0x50            | 28 |

| mem_slot_to_clocks[4]       | 0x014c       | 1 (4 total)    | RW     | See description | 28 |

| mem_spd[4]                  | 0x0150       | 64 (256 total) | RW     | All zeros       | 29 |

| io_port_debug_led           | 0x0254       | 2              | RW     | 0x0000          | 29 |

| mem_freq_min                | 0x0256       | 1              | RW     | 0x05            | 30 |

| mem_freq_max                | 0x0257       | 1              | RW     | 0x0A            | 30 |

| rom_size_total              | 0x0258       | 2              | RW     | 0x0020          | 30 |

| rom_size_bios               | 0x025a       | 2              | RW     | 0x000B          | 30 |

| cms_main_start_block        | 0x025c       | 1              | RW     | 0x01            | 30 |

| cms_main_num_blocks         | 0x025d       | 1              | RW     | 0x0A            | 31 |

| cms_recovery_start_block    | 0x025e       | 1              | RW     | 0x0B            | 31 |

| cms_recovery_num_blocks     | 0x025f       | 1              | RW     | 0x0A            | 31 |

| upgrade_oem_id0             | 0x0260       | 4              | ТО     | Contact TMTA    | 31 |

| upgrade_oem_id1             | 0x0264       | 4              | RW     | 0x00000000      | 31 |

| upgrade_options             | 0x0268       | 4              | RW     | 0x00000000      | 32 |

| upgrade_virtual_rom_model   | 0x026c       | 4              | RW     | 0x00000101      | 32 |

| sclkdly_to_mem_frequency[4] | 0x0270       | 1 (4 total)    | RW     | See description | 32 |

| group_to_min_loads[4]       | 0x0274       | 1 (4 total)    | RW     | See description | 32 |

| group_to_max_loads[4]       | 0x0278       | 1 (4 total)    | RW     | See description | 33 |

| longrun_frequencies[8]      | 0x027C       | 2 (16 total)   | RW     | See description | 33 |

### vr\_100mV\_ramp\_time

| Field Name         | Table Offset | Width (bytes) | Access | Default Value |

|--------------------|--------------|---------------|--------|---------------|

| vr_100mV_ramp_time | 0x0100       | 2             | RW     | 0x0023        |

Time in microseconds required to ramp voltage up or down by 100mV.

### vr\_voltage[32]

| Field Name     | Table Offset | Width (bytes) | Access | Default Value   |

|----------------|--------------|---------------|--------|-----------------|

| vr_voltage[32] | 0x0104       | 2 (64 total)  | RW     | See description |

An array of 32 fields which stores the voltage (in millivolts) associated with the corresponding VRDA value. The default values (in decimal) are as follows:

| Field          | Default Value |

|----------------|---------------|

| vr_voltage[0]  | 1750          |

| vr_voltage[1]  | 1700          |

| vr_voltage[2]  | 1650          |

| vr_voltage[3]  | 1600          |

| vr_voltage[4]  | 1550          |

| vr_voltage[5]  | 1500          |

| vr_voltage[6]  | 1450          |

| vr_voltage[7]  | 1400          |

| vr_voltage[8]  | 1350          |

| vr_voltage[9]  | 1300          |

| vr_voltage[10] | 1024          |

| vr_voltage[11] | 1200          |

| vr_voltage[12] | 1150          |

| vr_voltage[13] | 1100          |

| vr_voltage[14] | 1050          |

| vr_voltage[15] | 1000          |

| Field          | Default Value |

|----------------|---------------|

| vr_voltage[16] | 975           |

| vr_voltage[17] | 950           |

| vr_voltage[18] | 925           |

| vr_voltage[19] | 900           |

| vr_voltage[20] | 875           |

| vr_voltage[21] | 850           |

| vr_voltage[22] | 825           |

| vr_voltage[23] | 800           |

| vr_voltage[24] | 775           |

| vr_voltage[25] | 750           |

| vr_voltage[26] | 725           |

| vr_voltage[27] | 700           |

| vr_voltage[28] | 675           |

| vr_voltage[29] | 650           |

| vr_voltage[30] | 625           |

| vr_voltage[31] | 600           |

Also see longrun\_frequencies[8] on page 33 and longrun\_manifold[8] on page 39.

#### cpu\_feature

| Field Name  | Table Offset | Width (bytes) | Access | Default Value |

|-------------|--------------|---------------|--------|---------------|

| cpu_feature | 0x0144       | 4             | RW     | 0x00000002    |

CPU feature control bits.

| Bits | Name              | Function Description                                                                                                                                                                                              | Default |

|------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| 31:3 |                   | Reserved                                                                                                                                                                                                          | 0       |

| 2    | SSTL2_termination | <b>SSTL2 Termination</b> —If set, SSTL_2 termination is in use for the DRAM bus.                                                                                                                                  |         |

| 1    | disable_ecc       | Disable ECC—If set, treat ECC memory as non-ECC memory.                                                                                                                                                           | 1       |

| 0    | psn_disable       | PSN Disable—Permanently disable the processor serial number (PSN). Default is 0 (enable PSN). This feature is normally controlled via the Virtual Northbridge (VNB); for details see the BIOS Programmer's Guide. | 0       |

### cms\_memory\_size

| Field Name      | Table Offset | Width (bytes) | Access | Default Value |

|-----------------|--------------|---------------|--------|---------------|

| cms_memory_size | 0x0148       | 1             | RW     | 0x20          |

Size of memory (in MB) reserved for CMS usage.

#### mem\_probe\_spd

| Field Name    | Table Offset | Width (bytes) | Access | Default Value |

|---------------|--------------|---------------|--------|---------------|

| mem_probe_spd | 0x0149       | 1             | RW     | 0x03          |

Any bank that has mem\_slot\_to\_clocks (see below) clear is ignored. Otherwise, for any bank which has a set bit in this field, the memory configuration code attempts to probe for an SPD ROM.

When the appropriate bit is 1, if an SPD is found, it is used. Otherwise the slot is assumed to be empty. The only way to use SPD data from the OEM config table is to have the relevant mem\_probe\_spd field set to 0.

#### mem\_smbus\_spd\_base\_addr

| Field Name              | Table Offset | Width (bytes) | Access | Default Value |

|-------------------------|--------------|---------------|--------|---------------|

| mem_smbus_spd_base_addr | 0x014a       | 1             | RW     | 0x50          |

Address of first SPD ROM on the SMBUS.

#### mem\_slot\_to\_clocks[4]

| Field Name            | Table Offset | Width (bytes) | Access | Default Value   |

|-----------------------|--------------|---------------|--------|-----------------|

| mem_slot_to_clocks[4] | 0x014c       | 1 (4 total)   | RW     | See description |

This table of 4 fields maps DDR DIMM slot numbers to the clocks needed for that DIMM.

| Field                 | Default Value |

|-----------------------|---------------|

| mem_slot_to_clocks[0] | 0x07          |

| mem_slot_to_clocks[1] | 0x38          |

| mem_slot_to_clocks[2] | 0x00          |

| mem_slot_to_clocks[3] | 0x00          |

### mem\_spd[4]

| Field Name | Table Offset | Width (bytes)  | Access | Default Value |

|------------|--------------|----------------|--------|---------------|

| mem_spd[4] | 0x0150       | 64 (256 total) | RW     | All zeros     |

An array of SPD data for each DDR DIMM (soldered down or override). One mem\_spd field exists for each DDR memory bank. SDR memory is not supported. Default values are zero for all sub-fields.

The structure for each field is shown below. SPD fields contained in each mem\_spd field correspond directly with those described in the SPD specification. See the specification for more information on individual fields. Note that only the first 64 bytes of SPD data are used.

| Offset in<br>Structure | Size<br>(bytes) | SPD Field     |

|------------------------|-----------------|---------------|

| 0 0x0000               | 1               | written_bytes |

| 1 0x0001               | 1               | total_bytes   |

| 2 0x0002               | 1               | memory_type   |

| 3 0x0003               | 1               | row_addrs     |

| 4 0x0004               | 1               | col_addrs     |

| 5 0x0005               | 1               | phys_banks    |

| 6 0x0006               | 2               | dwidth        |

| 8 0x0008               | 1               | vIvI          |

| 9 0x0009               | 1               | tckmin        |

| 10 0x000a              | 1               | tac           |

| 11 0x000b              | 1               | dimmconf      |

| 12 0x000c              | 1               | ref           |

| 13 0x000d              | 1               | width         |

| 14 0x000e              | 1               | eccwidth      |

| 15 0x000f              | 1               | mindelay      |

| 16 0x0010              | 1               | blength       |

| 17 0x0011              | 1               | nbanks        |

| 18 0x0012              | 1               | cl            |

| 19 0x0013              | 1               | csl           |

| 20 0x0014              | 1               | wl            |

| 21 0x0015              | 1               | modflags      |

| 22 0x0016              | 1               | genflags      |

|                        | T               | T          |

|------------------------|-----------------|------------|

| Offset in<br>Structure | Size<br>(bytes) | SPD Field  |

| 23 0x0017              | 1               | tckmin1    |

| 24 0x0018              | 1               | tac1       |

| 25 0x0019              | 1               | tckmin2    |

| 26 0x001a              | 1               | tac2       |

| 27 0x001b              | 1               | trp        |

| 28 0x001c              | 1               | trrd       |

| 29 0x001d              | 1               | trcd       |

| 30 0x001e              | 1               | tras       |

| 31 0x001f              | 1               | density    |

| 32 0x0020              | 1               | tas        |

| 33 0x0021              | 1               | tah        |

| 34 0x0022              | 1               | tds        |

| 35 0x0023              | 1               | tdh        |

| 36 0x0024              | 1               | vcsdram[5] |

| 41 0x0029              | 1               | trc        |

| 42 0x002a              | 1               | trfc       |

| 43 0x002b              | 1               | tckmax     |

| 44 0x002c              | 1               | tdqsqmax   |

| 45 0x002d              | 1               | tqhs       |

| 46 0x002e              | 1               | tpll       |

| 62 0x003e              | 1               | rev        |

| 63 0x003f              | 1               | checksum   |

#### io\_port\_debug\_led

| Field Name        | Table Offset | Width (bytes) | Access | Default Value |

|-------------------|--------------|---------------|--------|---------------|

| io_port_debug_led | 0x0254       | 2             | RW     | 0x0000        |

I/O port address that forwards debug LED codes (0 to disable).

### mem\_freq\_min

| Field Name   | Table Offset | Width (bytes) | Access | Default Value |

|--------------|--------------|---------------|--------|---------------|

| mem_freq_min | 0x0256       | 1             | RW     | 5             |

Lower limit of memory frequency in 100/6 MHz increments.

#### mem\_freq\_max

| Field Name   | Table Offset | Width (bytes) | Access | Default Value |

|--------------|--------------|---------------|--------|---------------|

| mem_freq_max | 0x0257       | 1             | RW     | 10            |

Upper limit of memory frequency in 100/6 MHz increments.

#### rom\_size\_total

| Field Name     | Table Offset | Width (bytes) | Access | Default Value |

|----------------|--------------|---------------|--------|---------------|

| rom_size_total | 0x0258       | 2             | RW     | 0x0020        |

Total size of ROM for partitioning (in units of 64K).

#### rom\_size\_bios

| Field Name    | Table Offset | Width (bytes) | Access | Default Value |

|---------------|--------------|---------------|--------|---------------|

| rom_size_bios | 0x025a       | 2             | RW     | 0x000B        |

x86 BIOS size for partitioning (in units of 64K).

#### cms\_main\_start\_block

| Field Name           | Table Offset | Width (bytes) | Access | Default Value |

|----------------------|--------------|---------------|--------|---------------|

| cms_main_start_block | 0x025c       | 1             | RW     | 0x01          |

This field encodes how Code Morphing software is stored in the ROM. It refers to the first contiguous 64K block of Code Morphing software.

#### cms\_main\_num\_blocks

| Field Name          | Table Offset | Width (bytes) | Access | Default Value |

|---------------------|--------------|---------------|--------|---------------|

| cms_main_num_blocks | 0x025d       | 1             | RW     | 0x0A          |

This field encodes how Code Morphing software is stored in the ROM. It refers to the total number of contiguous 64K blocks of Code Morphing software.

#### cms\_recovery\_start\_block

| Field Name               | Table Offset | Width (bytes) | Access | Default Value |

|--------------------------|--------------|---------------|--------|---------------|

| cms_recovery_start_block | 0x025e       | 1             | RW     | 0x0B          |

This field encodes how recovery Code Morphing software is stored in the ROM. It refers to the first contiguous 64K block of recovery Code Morphing software.

#### cms\_recovery\_num\_blocks

| Field Name              | Table Offset | Width (bytes) | Access | Default Value |

|-------------------------|--------------|---------------|--------|---------------|

| cms_recovery_num_blocks | 0x025f       | 1             | RW     | 0x0A          |

This encodes how recovery Code Morphing software is stored in the ROM. It refers to the total number of contiguous 64K blocks of recovery Code Morphing software.

#### upgrade\_oem\_id0

| Field Name      | Table Offset | Width (bytes) | Access | Default Value |

|-----------------|--------------|---------------|--------|---------------|

| upgrade_oem_id0 | 0x0260       | 4             | ТО     | Contact TMTA  |

A description of this field is reserved for a future edition of this document. Note that this field is NOT USABLE as of this writing—OEMs must use a value provided by Transmeta.

#### upgrade\_oem\_id1

| Field Name      | Table Offset | Width (bytes) | Access | Default Value |

|-----------------|--------------|---------------|--------|---------------|

| upgrade_oem_id1 | 0x0264       | 4             | RW     | 0x00000000    |

A description of this field is reserved for a future edition of this document

#### upgrade\_options

| Field Name      | Table Offset | Width (bytes) | Access | Default Value |

|-----------------|--------------|---------------|--------|---------------|

| upgrade_options | 0x0268       | 4             | RW     | 0x00000000    |

A description of this field is reserved for a future edition of this document

#### upgrade\_virtual\_rom\_model

| Field Name                | Table Offset | Width (bytes) | Access | Default Value |

|---------------------------|--------------|---------------|--------|---------------|

| upgrade_virtual_rom_model | 0x026c       | 4             | RW     | 0x00000101    |

Virtual ROM model description. A description of this field is reserved for a future edition of this document.

#### sclkdly\_to\_mem\_frequency[4]

| Field Name                  | Table Offset | Width (bytes) | Access | Default Value   |

|-----------------------------|--------------|---------------|--------|-----------------|

| sclkdly_to_mem_frequency[4] | 0x0270       | 1 (4 total)   | RW     | See description |

Table mapping sclkdly values to maximum memory frequencies (in increments of 16.67 MHz).

| Field                       | Default Value |

|-----------------------------|---------------|

| sclkdly_to_mem_frequency[0] | 7             |

| sclkdly_to_mem_frequency[1] | 10            |

| sclkdly_to_mem_frequency[2] | 255           |

| sclkdly_to_mem_frequency[3] | 255           |

### group\_to\_min\_loads[4]

| Field Name            | Table Offset | Width (bytes) | Access | Default Value   |

|-----------------------|--------------|---------------|--------|-----------------|

| group_to_min_loads[4] | 0x0274       | 1 (4 total)   | RW     | See description |

Table specifying how many chip loads in each signal group can be driven with drive strength set to 0 (min). It depends strongly on board capacitance.

| Field                 | Default Value |

|-----------------------|---------------|

| group_to_min_loads[0] | 0             |

| group_to_min_loads[1] | 0             |

| Field                 | Default Value |

|-----------------------|---------------|

| group_to_min_loads[2] | 0             |

| group_to_min_loads[3] | -1            |

#### group\_to\_max\_loads[4]

| Field Name            | Table Offset | Width (bytes) | Access | Default Value   |

|-----------------------|--------------|---------------|--------|-----------------|

| group_to_max_loads[4] | 0x0278       | 1 (4 total)   | RW     | See description |

Table specifying how many chip loads in each signal group can be driven with drive strength set to 7 (max). It depends weakly on board capacitance.

| Field                 | Default Value |

|-----------------------|---------------|

| group_to_max_loads[0] | 18            |

| group_to_max_loads[1] | 18            |

| group_to_max_loads[2] | 18            |

| group_to_max_loads[3] | 9             |

#### longrun\_frequencies[8]

| Field Name             | Table Offset | Width (bytes) | Access | Default Value   |

|------------------------|--------------|---------------|--------|-----------------|

| longrun_frequencies[8] | 0x027C       | 2 (16 total)  | RW     | See description |

Table specifying LongRun™ frequencies. Each entry is a frequency in MHz, or 0 for an 'empty' entry. The non-empty entries must be contiguous at the start of the array. There is space for 8 entries in the array. Empty entries are ignored. Frequencies must be in ascending order.

To set a LongRun point, place a frequency entry in this table. Corresponding voltages are computed by Code Morphing software. Pre-set defaults are shown below.

Also see *vr\_voltage[32]* on page 27, *longrun\_manifold[8]* on page 39, and *longrun\_min\_frequency* on page 40. To set this field, contact your Transmeta representative.

| Field                  | Default Value |

|------------------------|---------------|

| longrun_frequencies[0] | 400           |

| longrun_frequencies[1] | 533           |

| longrun_frequencies[2] | 667           |

| longrun_frequencies[3] | 800           |

| Field                  | Default Value |

|------------------------|---------------|

| longrun_frequencies[4] | 0             |

| longrun_frequencies[5] | 0             |

| longrun_frequencies[6] | 0             |

| longrun_frequencies[7] | 0             |

## 4.3 Transmeta SKU Fields

The fields summarized in the following table comprise a Transmeta SKU, which is a single tested package configuration that controls several aspects of Code Morphing software. Contact your Transmeta representative to obtain the proper settings for these fields.

Table 3: Transmeta SKU Fields

| Field Name                 | Table Offset | Width (bytes) | Access | Default Value   | Page |

|----------------------------|--------------|---------------|--------|-----------------|------|

| sku_flags                  | 0x0800       | 4             | TO     | 0x00000000      | 35   |

| bpctrl                     | 0x0804       | 4             | ТО     | 0x00000019      | 35   |

| ifctrl                     | 0x0808       | 4             | ТО     | 0x00000002      | 35   |

| mode_da_low_v_range        | 0x080C       | 4             | ТО     | 0x04420F23      | 35   |

| mode_da_high_v_range       | 0x0810       | 4             | ТО     | 0x04420F23      | 35   |

| mode_da_low_v_range_max_v  | 0x0814       | 2             | ТО     | 1100            | 36   |

| mode_da_high_v_range_min_v | 0x0816       | 2             | ТО     | 900             | 36   |

| sc_laconfig                | 0x0818       | 2             | ТО     | 0x0aa3          | 36   |

| sc_ltconfig                | 0x081A       | 2             | ТО     | 0x00a3          | 36   |

| mode_tlb                   | 0x081C       | 1             | ТО     | 0x02            | 36   |

| mode_wq                    | 0x081D       | 1             | ТО     | 0x02            | 36   |

| pm_tag_mode                | 0x081E       | 1             | ТО     | 0x05            | 37   |

| pm_data_mode               | 0x081F       | 1             | ТО     | 0x05            | 37   |

| mc_pll_mode                | 0x0820       | 2             | ТО     | 0x6400          | 37   |

| mc_core_clkdiv             | 0x0822       | 2             | ТО     | 0x0090          | 37   |

| mc_misc_mode               | 0x0824       | 2             | ТО     | 0x6985          | 37   |

| mc_elroy_clkdiv            | 0x0826       | 2             | ТО     | 0x0604          | 37   |

| longrun_pll_relock         | 0x0828       | 1             | ТО     | 0x14            | 38   |

| core_voltage               | 0x0829       | 1             | ТО     | 0x0E            | 38   |

| rd_dqsdly_temp_adjust      | 0x082A       | 1             | ТО     | 0x52            | 38   |

| wr_dqdly_temp_adjust       | 0x082B       | 1             | ТО     | 0x00            | 38   |

| longrun_manifold[8]        | 0x082C       | 6 (48 total)  | ТО     | See description | 39   |

| longrun_min_frequency      | 0x085C       | 2             | ТО     | 0x012c          | 40   |

| cspec_lim                  | 0x085E       | 1             | ТО     | 0x1b            | 40   |

| vc_full                    | 0x085F       | 1             | ТО     | 0x1e            | 40   |

| vc_priority                | 0x0860       | 1             | ТО     | 0x15            | 40   |

| vc_threshold               | 0x0861       | 1             | ТО     | 0x0e            | 40   |

| dc_enable                  | 0x0862       | 1             | ТО     | 0x03            | 41   |

| it_ena                     | 0x0863       | 1             | ТО     | 0x07            | 41   |

| pcctl                      | 0x0864       | 2             | ТО     | 0x03ef          | 41   |

| sc_cs                      | 0x0866       | 2             | ТО     | 0x02ff          | 41   |

| ap_esr_io_dly_ctl          | 0x0868       | 4             | ТО     | 0x1c30300       | 41   |

| volt_max                   | 0x086C       | 2             | ТО     | 1500            | 42   |

| volt_min                   | 0x086E       | 2             | ТО     | 750             | 42   |

| volt_cons_mult             | 0x0870       | 1             | ТО     | 0               | 42   |

### sku\_flags

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| sku_flags  | 0x0800       | 4             | ТО     | 0x00000000    |

Flags to set SKU-specific features, as described below. Please set this field to a value designated by Transmeta.

| Bits | Name                   | Description                                             | Default |

|------|------------------------|---------------------------------------------------------|---------|

| 31:3 |                        | Reserved                                                | 0       |

| 2    | enable_AGP_fast_write  | Enable AGP fast writes <sup>1</sup>                     | 0       |

| 1    | enable_AGP_4x          | Enable AGP 4x <sup>1</sup>                              | 0       |

| 0    | enable_elroy_pll_divby | Allow Northbridge to work at odd multiples of 16.67 MHz | 0       |

<sup>1.</sup> Note that BIOS can still disable this feature.

#### **bpctrl**

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| bpctrl     | 0x0804       | 4             | ТО     | 0x0000019     |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### ifctrl

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| ifctrl     | 0x0808       | 4             | TO     | 0x00000002    |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mode\_da\_low\_v\_range

| Field Name          | Table Offset | Width (bytes) | Access | Default Value |

|---------------------|--------------|---------------|--------|---------------|

| mode_da_low_v_range | 0x080C       | 4             | ТО     | 0x04420F23    |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mode\_da\_high\_v\_range

| Field Name           | Table Offset | Width (bytes) | Access | Default Value |

|----------------------|--------------|---------------|--------|---------------|

| mode_da_high_v_range | 0x0810       | 4             | ТО     | 0x04420F23    |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mode\_da\_low\_v\_range\_max\_v

| Field Name                | Table Offset | Width (bytes) | Access | Default Value |

|---------------------------|--------------|---------------|--------|---------------|

| mode_da_low_v_range_max_v | 0x0814       | 2             | TO     | 1100          |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mode\_da\_high\_v\_range\_min\_v

| Field Name                 | Table Offset | Width (bytes) | Access | Default Value |

|----------------------------|--------------|---------------|--------|---------------|

| mode_da_high_v_range_min_v | 0x0816       | 2             | TO     | 900           |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### sc\_laconfig

| Field Name  | Table Offset | Width (bytes) | Access | Default Value |

|-------------|--------------|---------------|--------|---------------|

| sc_laconfig | 0x0818       | 2             | ТО     | 0x0aa3        |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### sc\_Itconfig

| Field Name  | Table Offset | Width (bytes) | Access | Default Value |

|-------------|--------------|---------------|--------|---------------|

| sc_Itconfig | 0x081A       | 2             | TO     | 0x00a3        |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mode tlb

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| mode_tlb   | 0x081C       | 1             | ТО     | 0x02          |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mode\_wq

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| mode_wq    | 0x081D       | 1             | TO     | 0x02          |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### pm\_tag\_mode

| Field Name  | Table Offset | Width (bytes) | Access | Default Value |

|-------------|--------------|---------------|--------|---------------|

| pm_tag_mode | 0x081E       | 1             | ТО     | 0x05          |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### pm\_data\_mode

| Field Name   | Table Offset | Width (bytes) | Access | Default Value |

|--------------|--------------|---------------|--------|---------------|

| pm_data_mode | 0x081F       | 1             | ТО     | 0x05          |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mc\_pll\_mode

| Field Name  | Table Offset | Width (bytes) | Access | Default Value |

|-------------|--------------|---------------|--------|---------------|

| mc_pll_mode | 0x0820       | 2             | ТО     | 0x6400        |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mc\_core\_clkdiv

| Field Name     | Table Offset | Width (bytes) | Access | Default Value |

|----------------|--------------|---------------|--------|---------------|

| mc_core_clkdiv | 0x0822       | 2             | TO     | 0x0090        |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mc misc mode

| Field Name   | Table Offset | Width (bytes) | Access | Default Value |

|--------------|--------------|---------------|--------|---------------|

| mc_misc_mode | 0x0824       | 2             | ТО     | 0x6985        |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### mc\_elroy\_clkdiv

| Field Name      | Table Offset | Width (bytes) | Access | Default Value |

|-----------------|--------------|---------------|--------|---------------|

| mc_elroy_clkdiv | 0x0826       | 2             | ТО     | 0x0604        |

Transmeta defined field. Please set this field to a value designated by Transmeta.

#### longrun\_pll\_relock

| Field Name         | Table Offset | Width (bytes) | Access | Default Value |

|--------------------|--------------|---------------|--------|---------------|

| longrun_pll_relock | 0x0828       | 1             | ТО     | 0x14          |

Value (in tenths of a microsecond) required for PLL relock during LongRun frequency change. Please set this field to a value designated by Transmeta.

#### core\_voltage

| Field Name   | Table Offset | Width (bytes) | Access | Default Value |

|--------------|--------------|---------------|--------|---------------|

| core_voltage | 0x0829       | 1             | TO     | 0x0E          |

Force core voltage used by boot code after reset, shown as VRDA code rather than a hardcoded mV value (see  $vr\_voltage[32]$  on page 27). Must be no higher than 50 mV higher than the lowest LongRun voltage, and must support 533 MHz core operation and 167 MHz Northbridge operation. Please set this field to a value designated by Transmeta.

#### rd\_dqsdly\_temp\_adjust

| Field Name            | Table Offset | Width (bytes) | Access | Default Value |

|-----------------------|--------------|---------------|--------|---------------|

| rd_dqsdly_temp_adjust | 0x082A       | 1             | ТО     | 0x52          |

Number of taps lost/gained per 50°C increment at Vmin. Two nibbles, the high nibble is taps lost at the high end, the low nibble is taps gained at the low end. Please set this field to a value designated by Transmeta.

#### wr\_dqdly\_temp\_adjust

| Field Name           | Table Offset | Width (bytes) | Access | Default Value |

|----------------------|--------------|---------------|--------|---------------|

| wr_dqdly_temp_adjust | 0x082B       | 1             | ТО     | 0x00          |

Number of taps lost/gained per 50°C increment at Vmin. Two nibbles, the high nibble is taps lost at the high end, the low nibble is taps gained at the low end. Please set this field to a value designated by Transmeta.

#### longrun\_manifold[8]

| Field Name          | Table Offset | Width (bytes) | Access | Default Value   |

|---------------------|--------------|---------------|--------|-----------------|

| longrun_manifold[8] | 0x082C       | 6 (48 total)  | TO     | See description |

This array of 8 fields contains a SKU which describes all supported LongRun voltage and frequency points. Not all 8 points are required; zeroes can be filled for unused points. The structure for each field is as follows:

| Offset in Structure | Width (bytes) | Value     | Units | Function Description                 |

|---------------------|---------------|-----------|-------|--------------------------------------|

| 0x0000              | 2             | frequency | MHz   | Frequency for this LongRun point     |

| 0x0002              | 2             | voltage   | mV    | Voltage for this LongRun point       |

| 0x0004              | 2             | temp      | °C    | Allowable temperature for this point |

It is important that non-empty entries have zero as their voltage (meaning that Code Morphing software computes the voltage), or all of them have non-zero values. All non-empty entries must be contiguous at the start of the array. There is space for 8 entries in the array.

There must be at least 3 non-empty entries in the longrun manifold for any system implementing LongRun Advanced Thermal Management:

- A top MHz entry at 80 (or 70) degrees C.

- Two different entries at 100 degrees C, one with high MHz (but presumably lower than the 80 degree entry), and one with low MHz, at or above 533 MHz.

For systems not implementing LongRun Advanced Thermal Management, at least two non-empty entries are necessary, namely the two entries at 100 degrees C described above. For more information about LongRun Advanced Thermal Management, see the documentation for the LR\_ATM register in the Transmeta Virtual Northbridge (VNB) in the *Efficeon TM8x00 BIOS Programmer's Guide*.

NOTE: To fix the frequency of operation, use the longrun frequencies[8] table on page 33, not the manifold.

Default values for this field are as follows.

| Field (frequency)          | Default |

|----------------------------|---------|

| longrun_point[0].frequency | 400     |

| longrun_point[1].frequency | 533     |

| longrun_point[2].frequency | 667     |

| longrun_point[3].frequency | 800     |

| longrun_point[4].frequency | 0       |

| longrun_point[5].frequency | 0       |

| longrun_point[6].frequency | 0       |

| longrun_point[7].frequency | 0       |

| Field (voltage)          | Default |

|--------------------------|---------|

| longrun_point[0].voltage | 1000    |

| longrun_point[1].voltage | 1100    |

| longrun_point[2].voltage | 1200    |

| longrun_point[3].voltage | 1250    |

| longrun_point[4].voltage | 0       |

| longrun_point[5].voltage | 0       |

| longrun_point[6].voltage | 0       |

| longrun_point[7].voltage | 0       |

| Field (temp)          | Default |

|-----------------------|---------|

| longrun_point[0].temp | 100     |

| longrun_point[1].temp | 100     |

| longrun_point[2].temp | 100     |

| longrun_point[3].temp | 80      |

| longrun_point[4].temp | 0       |

| longrun_point[5].temp | 0       |

| longrun_point[6].temp | 0       |

| longrun_point[7].temp | 0       |

Also see vr\_voltage[32] on page 27 and longrun\_frequencies[8] on page 33.

Note that LongRun will not set a frequency lower than the value shown in *longrun\_min\_frequency*, below, nor will it set voltages out of the range shown in *volt\_max* on page 42, *volt\_min* on page 42, and *volt\_cons\_mult* on page 42.

Please set this field to a value designated by Transmeta.

#### longrun\_min\_frequency

| Field Name            | Table Offset | Width (bytes) | Access | Default Value |

|-----------------------|--------------|---------------|--------|---------------|

| longrun_min_frequency | 0x085C       | 2             | TO     | 300           |

Minimum LongRun frequency, in MHz. Also see *volt\_max* on page 42, *volt\_min* on page 42, and *volt\_cons\_mult* on page 42, as well as *longrun\_manifold[8]* above.

Please set this field to a value designated by Transmeta.

#### cspec\_lim

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| cspec_lim  | 0x085E       | 1             | TO     | 0x1b          |

Cached speculation limit modebits register. Please set this field to a value designated by Transmeta.

#### vc full

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| vc_full    | 0x085F       | 1             | ТО     | 0x1e          |

Victim Cache Full indicator threshold modebits register. Please set this field to a value designated by Transmeta.

#### vc\_priority

| Field Name  | Table Offset | Width (bytes) | Access | Default Value |

|-------------|--------------|---------------|--------|---------------|

| vc_priority | 0x0860       | 1             | ТО     | 0x15          |

Victim Cache drain Priority threshold modebits register. Please set this field to a value designated by Transmeta.

#### vc\_threshold

| Field Name   | Table Offset | Width (bytes) | Access | Default Value |

|--------------|--------------|---------------|--------|---------------|

| vc_threshold | 0x0861       | 1             | ТО     | 0x0e          |

Victim Cache drain Theshold modebits register. Please set this field to a value designated by Transmeta.

#### dc\_enable

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| dc_enable  | 0x0862       | 1             | ТО     | 0x03          |

Data Cache Enable modebits register. Please set this field to a value designated by Transmeta.

#### it\_ena

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| it_ena     | 0x0863       | 1             | ТО     | 0x07          |

I/O Transfer Enable modebits register. Please set this field to a value designated by Transmeta.

#### pcctl

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| pcctl      | 0x0864       | 2             | ТО     | 0x03ef        |

PC-unit control modebits register. Please set this field to a value designated by Transmeta.

#### SC CS

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| sc_cs      | 0x0866       | 2             | ТО     | 0x02ff        |

Secondary Cache Control modebits register. Please set this field to a value designated by Transmeta.

#### ap\_esr\_io\_dly\_ctl

| Field Name        | Table Offset | Width (bytes) | Access | Default Value |

|-------------------|--------------|---------------|--------|---------------|

| ap_esr_io_dly_ctl | 0x0868       | 4             | ТО     | 0x1c30300     |

AGP I/O buffer circuitry delay values. Please set this field to a value designated by Transmeta.

#### volt\_max

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| volt_max   | 0x086C       | 2             | ТО     | 1500          |

Maximum LongRun voltage, in mV. Also see <code>longrun\_min\_frequency</code> on page 40, <code>volt\_min</code> on page 42, and <code>volt\_cons\_mult</code> on page 42, as well as <code>longrun\_manifold[8]</code> on page 39. Please set this field to a value designated by Transmeta.

#### volt\_min

| Field Name | Table Offset | Width (bytes) | Access | Default Value |

|------------|--------------|---------------|--------|---------------|

| volt_min   | 0x086E       | 2             | ТО     | 750           |

Minimum LongRun voltage, in mV. Also see <code>longrun\_min\_frequency</code> on page 40, <code>volt\_min</code> on page 42, and <code>volt\_cons\_mult</code> on page 42, as well as <code>longrun\_manifold[8]</code> on page 39. Please set this field to a value designated by Transmeta.

#### volt\_cons\_mult

| Field Name     | Table Offset | Width (bytes) | Access | Default Value |